精煉解讀《編碼》第13-14章 二進(jìn)制減法器與1位存儲(chǔ)器

《編碼:隱匿在計(jì)算機(jī)軟硬件背后的語(yǔ)言》第13-14章深入揭示了計(jì)算機(jī)算術(shù)運(yùn)算與數(shù)據(jù)存儲(chǔ)的基礎(chǔ)機(jī)制,這兩章構(gòu)成了理解計(jì)算機(jī)核心架構(gòu)的重要橋梁。

在第13章《二進(jìn)制減法器》中,作者通過(guò)邏輯門(mén)電路的巧妙組合,展示了如何實(shí)現(xiàn)二進(jìn)制減法運(yùn)算。與加法器類似,減法器同樣基于布爾代數(shù)原理,但引入了關(guān)鍵的“借位”處理機(jī)制:

1. 半減器基礎(chǔ)單元由異或門(mén)和與非門(mén)構(gòu)成,可處理單bit減法并產(chǎn)生差值及借位信號(hào)

2. 全減器通過(guò)級(jí)聯(lián)設(shè)計(jì),能處理多bit二進(jìn)制數(shù)的連續(xù)減法運(yùn)算

3. 借位傳播邏輯通過(guò)進(jìn)位鏈的逆向思維,實(shí)現(xiàn)了與加法器相似的并行處理能力

這種將數(shù)學(xué)運(yùn)算轉(zhuǎn)化為物理電路的設(shè)計(jì)思想,正是計(jì)算機(jī)能夠自動(dòng)執(zhí)行算術(shù)運(yùn)算的本質(zhì)所在。

第14章《1位存儲(chǔ)器》則轉(zhuǎn)向了計(jì)算機(jī)的“記憶”能力探索。作者通過(guò)繼電器構(gòu)建的基本存儲(chǔ)單元,揭示了信息存儲(chǔ)的核心原理:

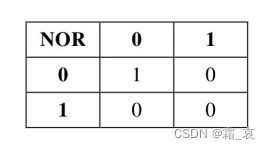

1. 設(shè)-復(fù)位觸發(fā)器(SR Latch)利用交叉耦合的或非門(mén)/與非門(mén),形成穩(wěn)定的雙穩(wěn)態(tài)電路

2. 時(shí)鐘信號(hào)引入的D觸發(fā)器實(shí)現(xiàn)了同步控制,避免競(jìng)爭(zhēng)冒險(xiǎn)現(xiàn)象

3. 單個(gè)存儲(chǔ)位的實(shí)現(xiàn)奠定了寄存器、內(nèi)存等存儲(chǔ)層次結(jié)構(gòu)的基石

這種能夠保持狀態(tài)的電路突破,使得計(jì)算機(jī)從純粹的計(jì)算工具進(jìn)化成為可存儲(chǔ)程序和數(shù)據(jù)的智能機(jī)器。

兩章內(nèi)容緊密銜接:減法器展現(xiàn)了計(jì)算機(jī)的運(yùn)算能力,而存儲(chǔ)器則賦予了計(jì)算機(jī)保持中間結(jié)果和程序狀態(tài)的能力。正是這些基礎(chǔ)組件的協(xié)同工作,才使得現(xiàn)代計(jì)算機(jī)能夠執(zhí)行復(fù)雜的序列操作,為后續(xù)章節(jié)中中央處理器(CPU)的誕生奠定了堅(jiān)實(shí)的理論基礎(chǔ)。從邏輯門(mén)到運(yùn)算器,從觸發(fā)器到存儲(chǔ)器,這條技術(shù)演進(jìn)路線清晰地勾勒出計(jì)算機(jī)從簡(jiǎn)單機(jī)械到智能設(shè)備的蛻變歷程。

如若轉(zhuǎn)載,請(qǐng)注明出處:http://www.dgsq.cn/product/33.html

更新時(shí)間:2026-02-04 19:15:40